# FB4XXVG@Z21D FPGA Card

## Quad Port SFP28 25 Gigabit FPGA Card

### **Product Description**

The FB4XXVG@Z21D is a high-performance OEM hardware platform intended for hardware acceleration for mobile 4G and 5G Baseband Units or Distributed Units with four SFP28 modules. Example: supports up to 16 100MHz carriers Radio Units via 4x 25G eCPRI/CPRI with SFP28 modules, as well as interfacing to a Grand master via SFP28 at 1/10/25G.

The card is based on a Xilinx® Zynq UltraScale+ RFSoC, which embeds a Processor System (PS) with four 64-bit Application Processing Units (ARM Cortex-A53) and two Real-Time Processing Units (ARM Cortex-R5) along with a powerful Programmable Logic (PL) part (UltraScale+ FPGA), as well as an integrated SD-FEC block.

The design is set to work in ORAN LLS-C1 and C2 with the intention to be utilized with a 4G/5G IP stack interfacing at 3GPP functional split options 8 for CPRI or 7.2x for eCPRI.

#### **Key Features**

- FPGA ZU21DR Speedgrade -1

- 4x SFP28 (1/10/25GB) (usable for PTP/sync)

- 1x 4GB DDR4 for Programmable Logic (FPGA)

- 1x 4GB DDR4 for Processing System (CPU)

- Dedicated HW for IEEE 1588 PTP support

- IEEE 1588

- Support for SyncE

- Support for extended holdover time with high stability clock OCXO

- GNSS receiver with bias for external antenna with 1x SMA connector or optional 1PPS input

- Optional secondary extension bracket with 2xSMA (1PPS In/out), 2xSMA (10MHz in+out)

- PCIe 3.0 x8

- Passive cooling (Active solution on request)

- Full height, Half length

#### **Technical Specifications**

| Network Interface |                                                                                                                                  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| IEEE standard     | IEEE 1588-2019                                                                                                                   |  |

| Interfaces        | <ul> <li>Physical interface: 4x SFP28</li> <li>Supported SFP28 and SFP+</li> <li>SMA connector to active GNSS Antenna</li> </ul> |  |

| Host Interface    |                                                                                                                                  |  |

| PCI bus           | 8 lanes PCle Gen1/Gen2/Gen3                                                                                                      |  |

**Connectivity Solutions**

| General Technical Specifications |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Configuration                    | <ul> <li>Upload of FPGA and SW code to flash via USB-JTAG</li> <li>Upload of FPGA and SW code to flash via micro-SD card</li> <li>Upload of FPGA and SW code to flash via PCIe host interface</li> <li>Support for encrypted FPGA bit file (optional)</li> </ul>                                                                |  |  |  |

| On-board Memory                  | <ul> <li>1x 4GB DDR4 (with ECC) for Programmable Logic (FPGA/PL)</li> <li>1x 4GB DDR4 (with ECC) for Processing System (CPU/PS)</li> </ul>                                                                                                                                                                                      |  |  |  |

| On-board Clock                   | <ul> <li>PCIe clock: 100 MHz (from host)</li> <li>Microsemi ZL30793 PLL</li> <li>PLL generated: Programmed</li> <li>OCXO for PTP</li> </ul>                                                                                                                                                                                     |  |  |  |

| RFSoC Versions Available         | <ul> <li>XCZU21DR—1FFVD1156E</li> <li>XCZU21DR—2FFVD1156E</li> </ul>                                                                                                                                                                                                                                                            |  |  |  |

| Environment                      | <ul> <li>Physical dimensions: Half length, standard height PCIe</li> <li>Power consumption: Max 65W</li> <li>Operating temperature: 0 – 55°C, 30 – 130°F</li> <li>Operating humidity: 20 – 80%, non-condensing</li> <li>Hardware compliance: RoHS, CE</li> <li>Passive cooling (no on-board fan required)</li> </ul>            |  |  |  |

| Additional Board Support         | <ul> <li>On-board temperature sensors</li> <li>Board status LEDs</li> <li>FPGA controlled Link and Activity LED for each port</li> <li>PPS clock synchronization connector (option)</li> <li>EEPROM storage</li> <li>Configurable PLL clock synthesizer (support for SyncE)</li> <li>10MHz high stability oscillator</li> </ul> |  |  |  |

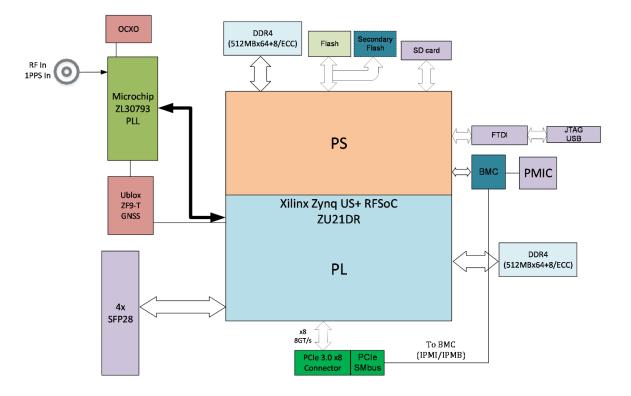

#### High Level Hardware Block Diagram

#### Description

Silicom Cassino Design employ a Xilinx RFSoC ZU21DR FPGA with no DAC/ADC hence optimized for High Phy (and Low Phy) implementation with 8 SD-FEC Cores for FEC Offload (LDPC, Turbo), by that freeing all the 930K System Logic Cells and 4272 DSP Slices for a layer 1 offload. The board is design with a 4GB (with the ability to expand to 8GB) DDR4 memory x72 (x64 with ECC) banks for PS and PL providing the user with enough memory for building deep FIFO. 4x SFP28 ports provides 25GbE connectivity to RRH with the support of PTP and SyncE while the Quad Core A53 enables PTP/1588 Termination on Smart NIC to ease system design.

| Feature                  | Description                                                                                                   | Notes                                                                                                   |

|--------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Form Factor              | PCIe Form Factor, Full Height;Half Length                                                                     |                                                                                                         |

| Cooling<br>Solution      | Passive                                                                                                       |                                                                                                         |

| Operating<br>Temperature | 0°C to +55°C                                                                                                  |                                                                                                         |

| NEBS                     | Level 3                                                                                                       |                                                                                                         |

| Ports                    | 4x SFP28                                                                                                      |                                                                                                         |

| Data Rate                | 10GbE and 25GbE Support<br>Fiber (25GBASE-SR, 25GBASE-LR,25GBASE-<br>CR), SFP(+/28) Direct Attach             |                                                                                                         |

| Host Interface           | PCle 3.0 x8                                                                                                   |                                                                                                         |

| FPGA                     | Xilinx ZU21DR -2/-1 SG                                                                                        |                                                                                                         |

| Memory                   | PS 4GB (with option for 8GB)<br>PL 4GB (with option for 8GB)                                                  |                                                                                                         |

| PLL                      | Microchip ZL30793                                                                                             |                                                                                                         |

| SMA                      | RF Input<br>1PPS Input                                                                                        | 1x SMA Connector, Dual function<br>Option - 1PPS In/Out and 10Mhz In/out on a<br>Separate metal bracket |

| GNSS                     | Ublox ZF9T                                                                                                    | Optional                                                                                                |

| OCXO                     | SiTimes SIT5721AC-KW333-T-10.00000T<br>MicroSemi OX-4011-EAE-0580-20M000<br>MicroSemi OX-2281-EAE-5000-20M000 | Only one of them is assembled                                                                           |

| BMC                      | Silicom Standard Gecko - Telemetry, Flash<br>Control, Power Sequencing                                        |                                                                                                         |

| Regulation               | CE, FCC Class B, ROHS, REACH, CMRT, UL                                                                        |                                                                                                         |

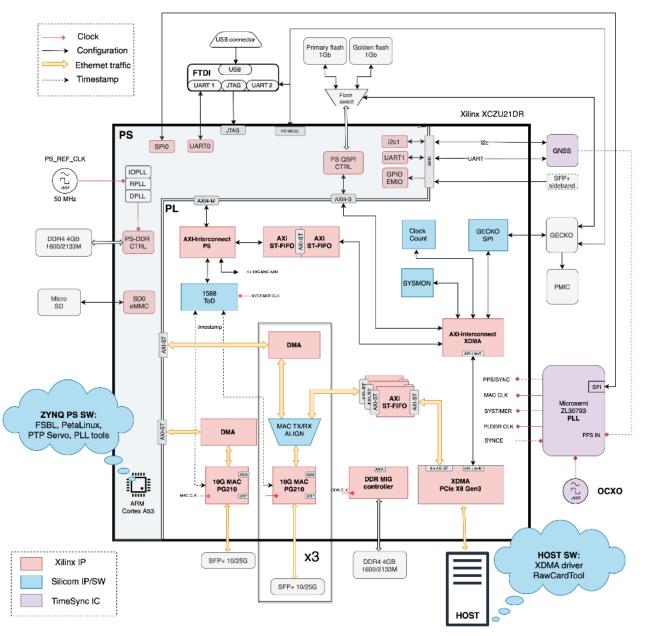

## Silicom Demo Design

Silicom Demo Design is a basic image Silicom provide with the hardware that serves as a start point for development.

- Full reference design with data wire to host

- Flash Programming from host over PCIe

- XDMA to PCIe Gen3

- 1 x Configuration AXI-Lite Master Interface: Access to the QSPI Flash device from HOST, accessing BMC and telemetry data from HOST, HOST to PS and PS to HOST file transfer

- 3 x AXI-ST interface: Streaming data packets between the front ports (SFP+ 10G) and HOST

#### **Features**

- 4x 25GbE/10GbE

- XDMA to PCIe

- PTP Time Stamp

- Memory Controller in PS/PL

- SD Card to PS for Debug

- PS Data path via 10G Ethernet ports

- AXI Interface

- I2C access via host SMBus

### **Cassino Deliverables**

#### Software Repository which includes

- Data Plane (PCIe)

- XDMA Driver

- Card Management tool

- BMC Board Management Controller

- Flash programming

- Monitoring

- Statistics and debug

- Xilinx Petalinux running on ARM Cores (PS)

- Time Synchronization PTP/1588 Stack and Servo SW (PS)

#### Hardware

- 1x Cassino card

- 1x USB cable (JTAG) optional

- 1x SMA Cable optional

- 1x SMA Bracket with 1PPS Input/Output and 10Mhz Input/Output optional

- 4x Fiber (25GBASE-SR, 25GBASE-LR, 25GBASE-CR), SFP(+/28) Direct Attach optional

### **Documentation**

- Hardware Specification

- Installation User Guide

- Demo Design User Guide

- SDK Reference Manual

- Petalinux User Guide

- Raw card tool Guide

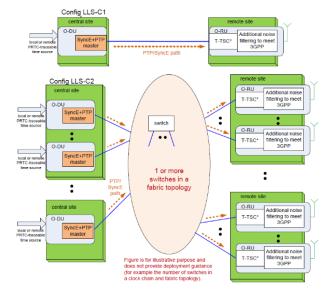

### **Cassino Time Synchronization Sub System**

#### **Standards**

- ORAN LLS-C1 and C2

- Support 1588/PTP over IPv4 / IPV6, IEEE1588v2

- Support SyncE /ITU-T G.8262

- T-BC/T-TSC Boundary Clock and TSC Slave Clock /G.8273.2

- OC Own Clock (Master / Slave) Class C (Stratum 3e)

- Support for Minimum 4Hours Hold Over

- Software 1588 Stack and Servo SW in ARM

#### Description

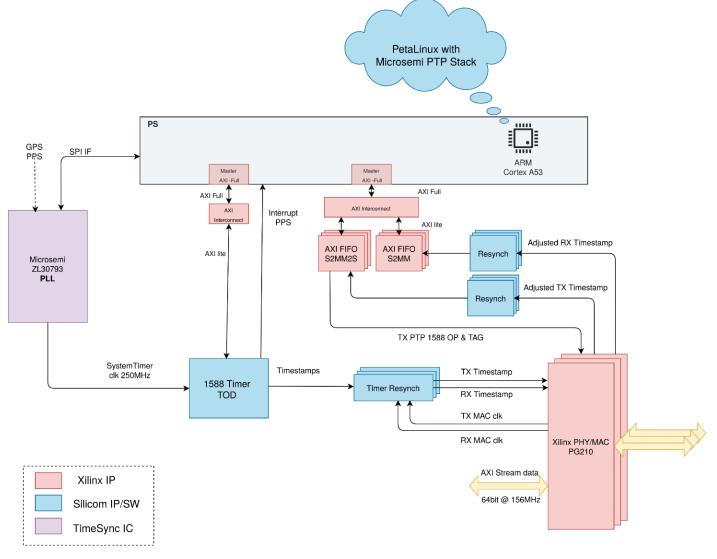

1588 Hardware time stamping reference design on 4x10G front port configuration:

- Support for *ptp4I* on Petalinux using the hardware timestamping features

- Support for phc2sys on PetaLinux to sync the Cassino RTC from the PTP clock

- Support for zIRegister on PetaLinux for Microsemi PLL register access

- Xilinx 10G Ethernet MAC+PCS/PMA 64-bit, Base-R with two step Timestamping Logic enabled, PG 210 v3.3

- *ToD* IP with *AXIL-4* interface, running on configurable clock frequency from the PLL.

- Timestamp synchronization from ToD clock to Ethernet clock domains

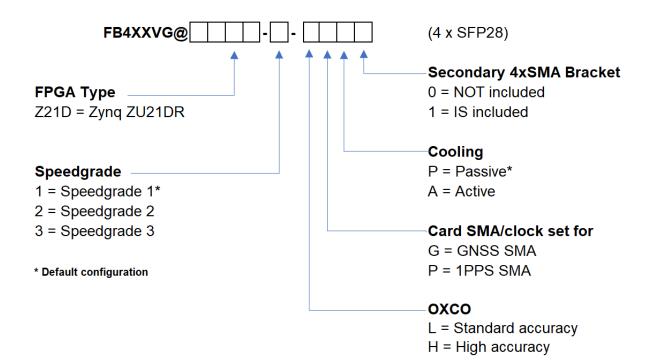

### **Cassino Ordering P/N**

| Product<br>Family | Product Description                                                                                                                                                                        | Ordering P/N        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Cassino           | FPGA PCIe card, 4xSFP28, ZU21DR FPGA SG-2,<br>Clock reference, HW IEEE1588/PTP, 1xSMA<br>GNSS, PCIe Gen3 X8,2x4GB DDR4, Passive<br>cooling, full height, ½ Length                          | FB4XXVG@Z21D-2-LGP0 |

| Cassino           | FPGA PCIe card, 4xSFP28, ZU21DR FPGA SG-2,<br>Clock reference, HW IEEE1588/PTP, 1xSMA PPS,<br>PCIe Gen3 X8,2x4GB DDR4, Passive cooling, full<br>height, <sup>1</sup> / <sub>2</sub> Length | FB4XXVG@Z21D-2-LPP0 |

| Cassino           | FPGA PCIe card, 4xSFP28, ZU21DR FPGA SG-2,<br>HQ Clock reference, HW IEEE1588/PTP, 1xSMA<br>GNSS, PCIe Gen3 X8,2x4GB DDR4, Passive<br>cooling, full height, ½ Length                       | FB4XXVG@Z21D-2-HGP0 |

| Cassino           | FPGA PCIe card, 4xSFP28, ZU21DR FPGA SG-2,<br>HQ Clock reference, HW IEEE1588/PTP, 1xSMA<br>PPS, PCIe Gen3 X8,2x4GB DDR4, Passive<br>cooling, full height, ½ Length                        | FB4XXVG@Z21D-2-HPP0 |

### **Cassino Product Ordering Guide**

#### **Cassino Release Plan**

| Delivery<br>Date                     | Deliverable                              | Description                                                                                                                                        |

|--------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| January<br>11 <sup>th</sup> , 2021   | First Customer Release                   | Version for 4x10G, network connectivity and<br>xDMA server connectivity supplied<br>Initial Hardware Design verification successfully<br>completed |

| February<br>5 <sup>th</sup> , 2021   | First Customer IP porting<br>complete    | First release evaluation completed in collaboration with beta customers.                                                                           |

| June 16 <sup>th</sup> ,<br>2021      | Samples of revision 2 ready for shipment | Revision 2 hardware and upgraded board support<br>package including FPGA reference design<br>including 1588 "as-is" and PetaLinux 2020.2.          |

| July 16 <sup>th</sup> ,<br>2021      | General Availability revision 2          | Pre-NEBS report completed. Available production volume limited due to component lead-times                                                         |

| September<br>30 <sup>th</sup> , 2021 | Start full volume production             |                                                                                                                                                    |

#### www.silicom-usa.com

Silicom Ltd. International Headquarters 14 Atir Yeda St. Kfar Sava 4464323 Israel Tel: (972)-9-764-4555 Silicom Connectivity Solutions Inc. USA Office 6 Forest Ave, Paramus New Jersey 07652 USA Tel: 18004silicom (Toll Free no.)

#### www.silicom.dk

Silicom Denmark A/S Poppelgaardvej 11 DK-2860 Soeborg Denmark Phone +45 46 32 74 55 contactus@silicom.dk